# Overview

This document is the application notes about the design of 2CG series.

The example of application circuits and parts value which are indicated to this application note aim at assistance of a design.

Therefore, external parts variation or user operating conditions are not fully taken into consideration.

Please take parts variation, operating conditions into consideration when designing.

# Contents

| 1. Application Examples                                                              | 2  |

|--------------------------------------------------------------------------------------|----|

| 1.1 Si-IGBT,SiC-MOSFET <2CG_B_Direct mode>                                           | 2  |

| 1.2 Si-IGBT,SiC-MOSFET <2CG_B_Half bridge mode>                                      | 2  |

| 1.3 SiC-MOSFET <2CG-D_Direct mode>                                                   | 3  |

| 1.4 SiC-MOSFET <2CG-D_Half bridge mode mode>                                         | 3  |

| 2. Pin Functions and Descriptions                                                    | 4  |

| 2.1 Pin Functions                                                                    | 4  |

| 2.2 Description                                                                      | 8  |

| 3. Product Connection Instructions, Ambient Environment Instructions, Usage Cautions | 11 |

| 3.1 Abnormal input current protection                                                | 11 |

| 3.2 VIN- and GND 1                                                                   | 11 |

| 3.3 Mechanical switch                                                                | 11 |

| 3.4 Input signals                                                                    | 11 |

| 3.5 Half bridge mode                                                                 | 11 |

| 3.6 Input cables 1                                                                   | 12 |

| 3.7 Wiring of the DC/DC converter                                                    | 12 |

| 3.8 DESAT protection circuit                                                         | 13 |

| 3.9 Gate resistors selection method                                                  | 14 |

| 3.10 Peripheral board design, wiring, and setting for the module                     | 14 |

| 3.11 Handling 1                                                                      | 16 |

| 3.12 Device short circuit                                                            | 16 |

| 3.13 Ambient temperature instructions 1                                              | 16 |

|                                                                                      |    |

# 1. Application Examples

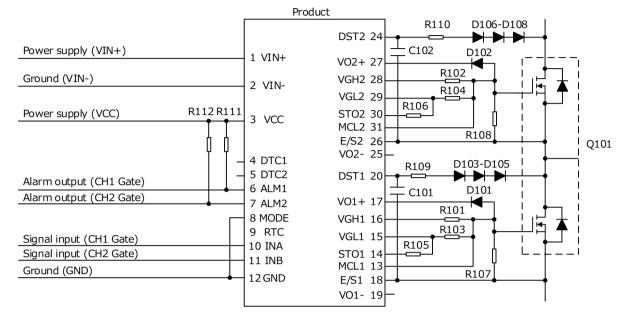

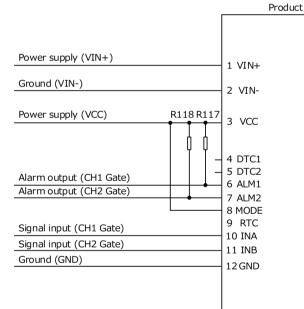

# 1.1 Si-IGBT, SiC-MOSFET < 2CG\_B\_Direct mode>

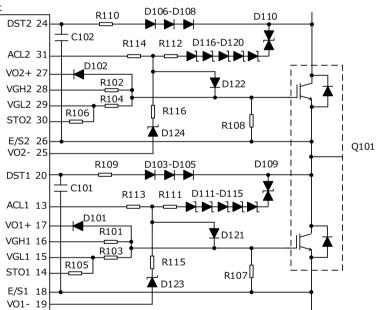

# 1.2 Si-IGBT,SiC-MOSFET <2CG\_B\_Half bridge mode>

|                                                                    | Product                                       |

|--------------------------------------------------------------------|-----------------------------------------------|

|                                                                    |                                               |

| Power supply (VIN+)                                                | 1 VIN+                                        |

| Ground (VIN-)                                                      | 2 VIN-                                        |

| Power supply (VCC) R112 R111                                       | 3 VCC                                         |

| Alarm output (CH1 Gate)                                            | 4 DTC1<br>5 DTC2<br>6 ALM1<br>7 ALM2          |

| Signal input (CH1 Gate)<br>Signal input (CH2 Gate)<br>Ground (GND) | 8 MODE<br>9 RTC<br>10 INA<br>11 INB<br>12 GND |

| -                                        |                                                                       |          |           |

|------------------------------------------|-----------------------------------------------------------------------|----------|-----------|

| DST2 24                                  | R110 D106-D108                                                        | •        |           |

| VO2+ 27<br>VGH2 28<br>VGL2 29<br>STO2 30 | C102 D102<br>R102 R104 R106                                           |          |           |

| MCL2 31<br>E/S2 26<br>VO2- 25            | R108                                                                  |          | Q101      |

| DST1 20                                  | R109 D103-D105                                                        |          | <br> <br> |

| VO1+ 17                                  | $\begin{array}{c c} \hline C101 \\ \hline R101 \\ \hline \end{array}$ | <b>—</b> | <br>      |

| VGH1 16                                  |                                                                       |          |           |

| VGL1 15                                  | R105                                                                  |          |           |

| STO1 14<br>MCL1 13                       |                                                                       |          |           |

| E/S1 18                                  | R107                                                                  | •        |           |

| VO1- 19                                  | - I                                                                   |          |           |

1.1, 1.2 Parts example

| Symblo   | Description | Part No.    | Manufacture |

|----------|-------------|-------------|-------------|

| Q101     |             |             |             |

| D101,102 | Diode       | RB400VAM-50 | ROHM        |

| D103-108 | Diode       | CMF05       | TOSHIBA     |

| C101,102 | Capacitor   | 100pF 25V   |             |

| Γ | Symblo   | Description | Part No.    | Remark       |

|---|----------|-------------|-------------|--------------|

|   | R101-104 | Resistor    | 0.51Ω 4W    | Refer to P14 |

|   | R105,106 | Resistor    | 18Ω 0.75W   | Refer to P14 |

| ſ | R107,108 | Resistor    | 10kΩ 0.125W |              |

| ſ | R109,110 | Resistor    | 100Ω 0.1W   | Refer to P13 |

|   | R111,112 | Resistor    | 10kΩ 0.1W   |              |

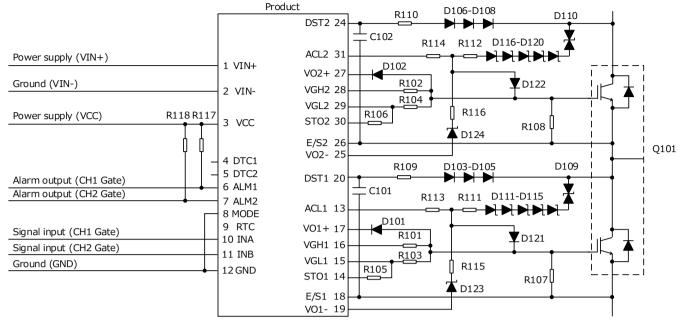

# 1.3 SiC-MOSFET <2CG-D\_Direct mode>

# 1.4 SiC-MOSFET <2CG-D\_Half bridge mode mode>

#### 1.3, 1.4 Parts example

| Symblo           | Description | Part No.    | Manufacture |

|------------------|-------------|-------------|-------------|

| Q101             |             |             |             |

| D101,102         | Diode       | RB400VAM-50 | ROHM        |

| D103-108         | Diode       | CMF05       | TOSHIBA     |

| D109,110         | TVS Diode   | P6SMB250CA  | Diotec      |

| D111-113,116-118 | TVS Diode   | P6SMB250A   | Diotec      |

| D114,115,119,120 | TVS Diode   | P6SMB220A   | Diotec      |

| D121,122         | Diode       | RB162MM-40  | ROHM        |

| D123,124         | Diode       | KDZV20B     | ROHM        |

| Symblo   | Description | Part No.    | Remark       |

|----------|-------------|-------------|--------------|

| C101,102 | Capacitor   | 100pF 25V   |              |

| R101-104 | Resistor    | 0.51Ω 4W    | Refer to P14 |

| R105,106 | Resistor    | 18Ω 0.75W   | Refer to P14 |

| R107,108 | Resistor    | 10kΩ 0.125W |              |

| R109,110 | Resistor    | 100Ω 0.1W   | Refer to P13 |

| R111,112 | Resistor    | 0Ω          | Refer to P9  |

| R113,114 | Resistor    | 1kΩ 0.1W    | Refer to P9  |

| R115,116 | Resistor    | 4.7Ω 0.25W  | Refer to P9  |

| R117,118 | Resistor    | 10kΩ 0.1W   |              |

# 2. Pin Functions and Descriptions

## 2.1 Pin Functions

- (1) VIN(+), VIN(-) (Power supply pin for DC/DC converter)

- (2) VCC (Power supply pin for drive circuit)

- (3) GND (Ground pin for drive circuit)

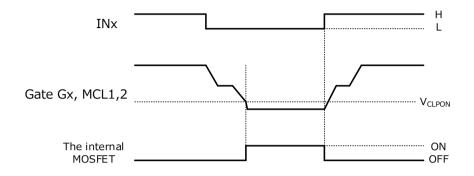

- (4) MOD, INA, INB (Mode switching pin, Control input pin)

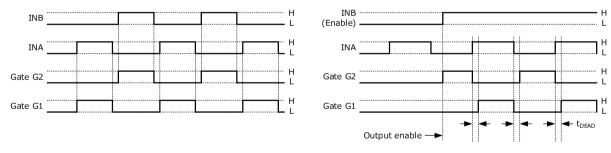

The INA, INB and MOD pin is a pin used to determine output logic.

Direct mode / Half bridge mode can be switched by MOD pin.

In Half bridge mode, it functions as INA: gate signal, INB: enable signal.

If INA or INB is not used, please be connected to GND

| MOD                                    | INB | INA | Gate G2 | Gate G1 | Mode             |

|----------------------------------------|-----|-----|---------|---------|------------------|

| L<br>(Floating or<br>Connected to GND) | Х   | L   | Х       | L       |                  |

|                                        | Х   | Н   | Х       | Н       | Direct mode      |

|                                        | L   | Х   | L       | Х       | Direct mode      |

|                                        | Н   | Х   | Н       | Х       |                  |

| н                                      | L   | Х   | L       | L       |                  |

| (Connected to VCC)                     | Н   | L   | Н       | L       | Half bridge mode |

|                                        | Н   | Н   | L       | Н       |                  |

\*\*Gate G1 : Gate output of CH1 side Gate G2 : Gate output of CH2 side

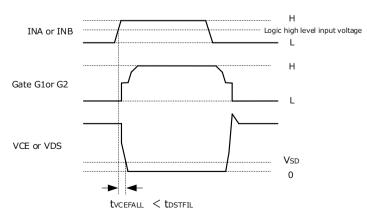

Timing chart of Direct mode

# (5) ALM1,2 (Alarm signal output pin)

When abnormality occurs (UVLO, short circuit detected), This pin outputs an alarm signal. (Open drain)

| Status                                                              | ALM1,2 |

|---------------------------------------------------------------------|--------|

| While in normal operation                                           | Hi-Z   |

| UVLO, When detecting short circuit, When Gate-Emitter short circuit | L      |

When using this function, connect a pull-up resistor because it is an open drain output.(Refer to Figure 1.1 R110,R111)

| Pull-up voltage [V] | Pull-up resistor [kΩ] |

|---------------------|-----------------------|

| 5                   | 4.7                   |

| 15                  | 15                    |

Timing chart of Half bridge mode

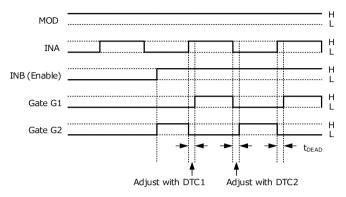

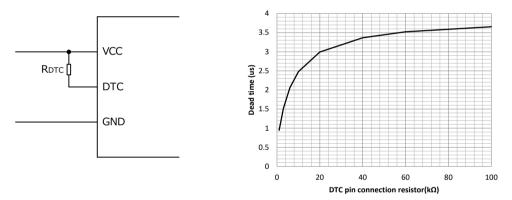

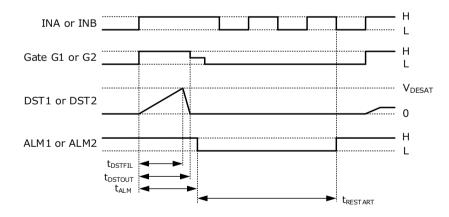

(6) DTC1,2  $\cdot$   $\cdot$  Dead time adjustment pin

When half-bridge mode, this pin is adjust the dead time of gate output G1,G2.

When not in use, connection to other circuits is impossible.

If you want to adjust dead time at half-bridge mode, please refer to the figure below.

Timing chart of Half bridge mode

#### ① Adjustment by resistor

The restart time can be adjusted by adding a resistor between VCC and DTC.

#### Adjustment by capacitor

The restart time can be adjusted by adding a capacitor between DTC and GND.

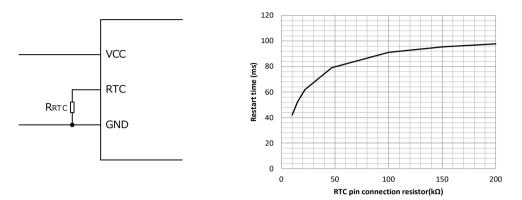

## (7) RTC (Recovery time of protection circuit control pin)

When abnormality occurs (UVLO, short circuit detected), this pin is used to adjust the recovery time.

When not in use, do not connect to other circuits.

The restart time can be adjusted within the following range by the resistance or voltage connected to the RTC pin.

# ① Adjustment by resistor

The restart time can be adjusted by adding a resistor between RTC and GND.

# Adjustment by voltage

The restart time can be adjusted by applying a voltage between RTC and GND.

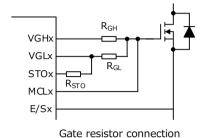

- (8) VGH1,2(Gate ON side pin)

- (9) VGL1,2(Gate OFF side pin)

# (10) E/S1,2(Emitter/source pin)

(11) STO1,2(Soft turn off pin)

The STO pin is a pin for gradually decrease gate voltage in operating desaturation protection. STO pin connect to the gate pin though a resistance value higher than the resistance value connected to VGL 1 and 2. Recommend  $10\Omega$  to  $47\Omega$ .

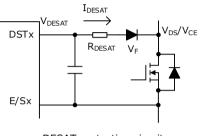

# (12) DST1,2(DESAT detection pin)

The DESAT pin is a pin used to detect desaturation of IGBT/MOSFET. When the DESAT pin voltage exceeds VDESAT, function will be activated. This may cause the IC to malfunction in an open state.

To avoid such trouble, short-circuit the DESAT pin to the E/S pin if the desaturation protection is not used.

For the noise mask time t<sub>DESATFIL</sub> in order to prevent the wrong detection due to noise is set, please connect a capacitor between DSTx and E/S.

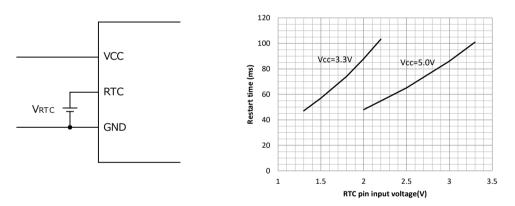

## (13) VO1+,VO2+,VO1-,VO2(DC/DC converter output pin)

The VO1+,VO2+,VO1-,VO2- pin is a output pin of built-in DC/DC converter. If necessary, connect a capacitor. When Q is large, adding a capacitor to VOx+ and VOx- stabilizes the gate output characteristic. Connect as refer to the figure below, if necessary. the capacitor of Maximum connectable is 470uF or less.

| Unit No.     | $C_{VO+}$ : $C_{VO-}$ |

|--------------|-----------------------|

| 2CG010xBC11N | 1:1                   |

| 2CG010xBC12N | 1:1                   |

| 2CG010BBC13N | 1:2                   |

| 2CG010BBC14N | 1:4                   |

ex) 2CG010BBC13N CVO+ : CVO- = 4.7uF : 10uF

External output capacitor

# (14) MCL1,2(Miller clamp pin) - 2CG-B series only

The MCL pin is a pin for preventing increase in gate voltage due to the miller current of t he power deviceconnected to Gate pin. If not use , shor-curcit between MCL1 and Vo1-, and between MCL1 and Vo2-, as there is a concern of malfunction due to noise.

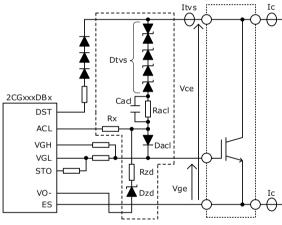

(15) ACL1,2(Active clamp pin) - 2CG-D series only

It is an active clamp terminal for raising the gate voltage when the TVS for active clamp is operating.

If not in use, open or connect to VOx-.

When the ACL pin rises to the ON voltage, the active clamp function operates and VGLx becomes High-Z. The time to operate the ACL pin should be Duty 2% or less. ACL pin.

| Gate Gx | ACL1,2 | VGLx   | STOx |

|---------|--------|--------|------|

| L       | L      | L      | L    |

| L       | Н      | High-Z | L    |

# 2.2 Description

(1) Overload protection function (DC / DC converter)

The overload protection function is protection when an output short circuit or overload occurs.

The operation mode is automatic reset operation.

Do not use beyond the maximum output power or permissible frequency curve as it may cause the gate voltage to drop.

(2) Overheat protection (DC / DC converter)

This module has an overheat protection function to prevent damage and smoke even if the module overheats for some reason. The operation mode is automatic reset operation.

Operation is auto restored when the internal temperature of the module becomes normal.

(3) Undervoltage Lockout (UVLO) function

The control circuit incorporates the undervoltage lockout (UVLO) function on the OUT(H) sides. When the OUT(H) voltage drops to the UVLO ON voltage, the Output pin and the ALM pin both will output the "L" signal. When the OUT(H) voltage rises to the UVLO OFF voltage, these pins will be reset.

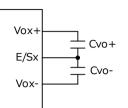

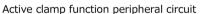

(4) Short circuit protection function, Soft turn-off function

When the DSTx pin voltage exceeds  $V_{DESAT}$ , the short circuit protection function will be activated.

When the short circuit protection function is activated, the gate ON/OFF side pin will be set to the "High-Z" level, the STOx pin will be set to the "L" level, and then the ALM pin voltage to the "L" level.

Also, soft turn-off function works to reduce collector/drain voltage surge due to short circuit current.

Short-circuit protection is canceled automatically after an abnormal condition restart time and when the input signal is "L" level.

Timing chart of short circuit protection function

(5) Active clamp function - 2CG-D series only

The active clamp function protects the IGBT from a sudden voltage surge between the collector and emitter that occurs when the IGBT is turned off by connecting the circuit as shown in the figure below. Depending on the DC-LINK voltage and surge voltage, the losses that occur in TVS diodes and IGBTs increase.

If a high surge voltage is clamped continuously, stress will be applied to the driver and IGBT. Therefore, the constant of TVS diode and the main circuit conditions (DC-LINK voltage, parasitic inductance, dIc / dt) should be optimized and designed so that the active clamp function does not operate in normal status. Design the TVS surface temperature not to exceed 120 ° C under any conditions. When the collector-gate voltage exceeds the breakdown voltage of the active clamp TVS diode, current flows from the collector to the gate. The current (Itvs) supplies the gate with charge, partially turning on the IGBT and clamping the collector voltage. TVS loss can be obtained by time integration of the current (Itvs) and collector-emitter voltage (Vce).

Depending on the set condition, the gate may rise even during the period when no current is flowing through the TVS diode, but this is not a malfunction.

Also, the minimum resistance (sink side) value to connect to VGLx is  $0.5\Omega$ , and a resistance value of 3/4 or more of the internal resistance value of the IGBT is recommended.

- -Dtvs : Set the TVS diode to a voltage that does not normally operate, and use at least one bidirectional TVS. Be careful of the power and temperature of the TVS. ex) DC-link voltage:  $800V \Rightarrow$  TVS total voltage: 850Vmin or more (including variation)

- -Racl, Cacl : Adjust the power loss of TVS diode and IGBT. Adjust according to evaluation. Be careful of the power of the resistor. ex) Racl =  $0 \sim 100\Omega$

- -Dacl : Set the voltage/current during clamping so that it does not exceed the rated value.

ex) Schottky barrier diode / VR: 30 V or more / IF: 1 A or more

- -Rx : his resistor adjusts the voltage applied to the ACLx pin of the gate driver.

An internal resistor of 1kΩ is placed between ACL pin and VO-pin of the gate driver module, so adjust it so that it does not exceed the rating.

Also, It is possible to adjust the timing at which the ACL function operates by detecting a rise in the Vce voltage.

Check and set the Eoff during normal operation and the Vce voltage at which the ACL function operates.

- -Rzd, Dzd : Protects Vge and ACLpin from overvoltage application when TVS diode is clamped. Set as necessary.

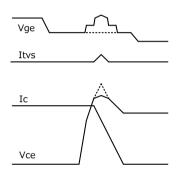

# (6) Miller clamp function - 2CG-B series only

If gate output Gx=L and the Miller clamp pin voltage  $< V_{CLPON}$ , the internal MOSFET for the miller clamp pin turns on.

| Gate Gx | MCL1,2                                 | Internal MOSFET for MCL pin |

|---------|----------------------------------------|-----------------------------|

| Н       | Х                                      | OFF                         |

| L       | Not less than $V_{\mbox{\tiny CLPON}}$ | OFF                         |

| L       | Less than $V_{\mbox{\tiny CLPON}}$     | ON                          |

Timing chart of Miller clamp function

# 3. Product Connection Instructions, Ambient Environment Instructions, Usage Cautions

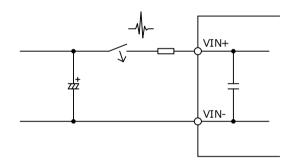

#### 3.1 Abnormal input current protection

Always mount fuse on the plus side of input for ensuring safety because the fuse is not built-in the product. Please select the fuse considering conditions such as steady current, inrush current, and ambient temperature. When using a fuse having large rated current or high capacity input electrolytic condenser, by combining another converter and input line and input electrolytic condenser, fuse may not blow off in the case of abnormality. Do not combine high voltage line and fuse.

# 3.2 VIN- and GND

Although VIN- and GND are insulated inside the product, they are not designed to be insulated according to safety standards. Connect on the set side so that there is no electric potential difference between VIN- and GND.

#### 3.3 Mechanical switch

Do not connect mechanical switches to the input line.

If a mechanical switch is required, add a rush-prevention resistor in series with the mechanical switch.

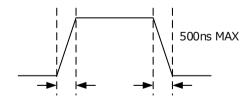

#### 3.4 Input signals

Make sure the rise/fall time of the input signal is 500ns or less.

Also, keep input wiring as far as possible from noise sources.

To prevent malfunction due to noise, we recommend the highest possible signal voltage within the recommended range.

## 3.5 Half bridge mode

The dead time set in half bridge mode is not highly accurate because it is set by the time constant of the capacitor and resistor. Select direct mode if more accurate operation is required.

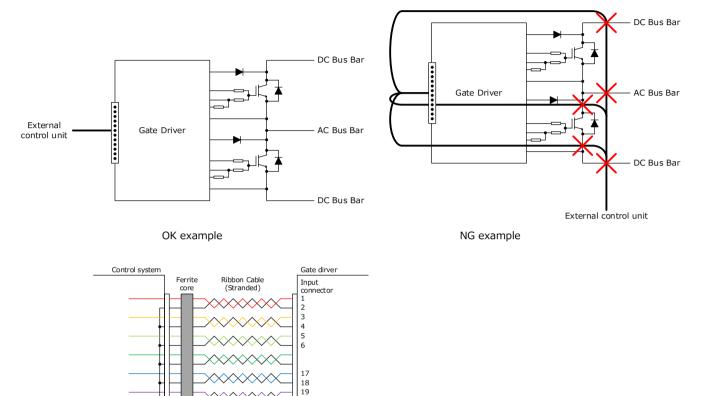

# 3.6 Input cables

Bringing the input cable of the product closer to the main circuit side will cause malfunction due to conduction noise and magnetic flux noise on the main circuit side. Therefore, place the input cable far from where these noises are likely to occur.

If the input cable of the product and the main circuit are close to each other due to space restrictions, we recommend changing the cable to be used to a ribbon cable (stranded wire type) or adding a ferrite core, or both.

Input cables(Wiring with lead wire)

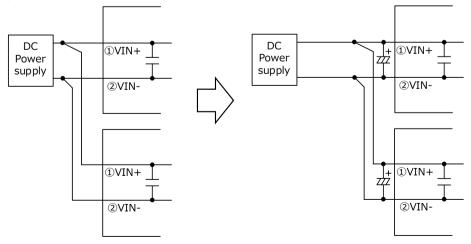

## 3.7 Wiring of the DC/DC converter

If multiple modules are driven and there is current flow of between adjacent modules, then wiring should branch from close to the power supply to each module. If it cannot branch from close to the power supply, measures such as adding a capacitor to the branch points should be taken.

20

# TAMURA CONFIDENTIAL/Preliminary

# 3.8 DESAT protection circuit

Detection voltage VSD, for which the DESAT protection function works, can be adjusted using VF of the high-voltage diode and RDESAT of the series-connected resistor. The high-voltage diode to be connected to DESAT must be selected according to the withstand voltages of the elements to be connected and the voltages applied to the elements. Connect 100  $\Omega$  or more to the DSTx pin to prevent damage.

Formula : Detection voltage  $V_{\text{SD}}$  =  $V_{\text{DESAT}}$  - (  $V_{\text{F}}$  +  $R_{\text{DESAT}}$   $\times$   $I_{\text{DESAT}}$  )

The voltage equal to VDS/VCE is impressed on a high-voltage diode. For working voltage, take care to ensure a withstand voltage margin.

DESAT protection circuit

Detection voltage V\_{SD} = VDESAT - ( VF + RDESAT  $\times$  IDESAT ) = 6.35V - ( 2V + 100 $\Omega$   $\times$  0.24mA )  $\doteqdot$  4.33V

Also, DESAT detection filter time ( $t_{DSTFIL}$ ) can be adjusted by  $C_{DESAT}$  connected in parallel with DSTx pin and E/Sx.

$Formula \ : t_{\text{DSTFIL}} = \ C_{\text{DESAT}} \times V_{\text{DESAT}} \ / \ I_{\text{DESAT}}$

$t_{\text{DSTFIL}} = \, C_{\text{DESAT}} \times \, V_{\text{DESAT}} \, / \, \, I_{\text{DESAT}} = \, 150 \text{pF} \times \, 6.35 \text{V} \, / \, 240 \text{uA} ~ \doteqdot ~ 3.97 \text{us}$

Adjust  $C_{\text{DESAT}}$  or Gate resistor as shown below to prevent DESAT protection malfunction in normal operation.

$t_{DSTFIL} > t_{VCEFALL}$

## 3.9 Gate resistors selection method

(1) Selecting gate resistors

When selecting a gate resistor, take into consideration surge voltage, noise, etc., of the elements to be connected. STOx pin connect a resistor  $R_{STO}$ , as shown below. During DESAT operation, the gate is pulled low by the resistance value of  $R_{GL}+R_{STO}$ . Adjust  $R_{STO}$  while checking the drain voltage/collector voltage and the time of short circuit current during short circuit.

%MCLx pin no connect, When not in use of miller clamp function.

(2) Maximum electric power and pulse capacity

Since pulse current flows through gate resistors, their pulse power capacity must be fully considered.

For the pulse capacity, contact the relevant resistor manufacturer(s).

The operating electrical power of resistors must be set to around 50% or less of their rated electrical power, and care must be taken for component temperatures during use. Recommended resistor surface temperature :  $120^{\circ}$  or less.

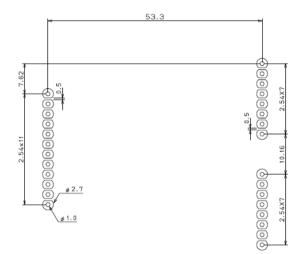

# 3.10 Peripheral board design, wiring, and setting for the module

(1) Recommended hole diameter, land size, and pin pitch

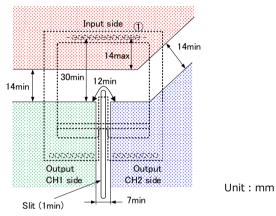

Component side view

$\boldsymbol{\cdot}$  Numbers with a circle are pin numbers

In order to ensure resistance to vibration and drop impact, provide all pins with a land, and solder them.

Unit : mm

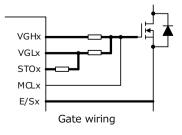

#### (2) Gate wiring

Pulse current flows through the part of the VGHx, VGLx and STOx pins indicated by bold lines in the figure below, and so the pattern of that part must be as thick and short as possible.

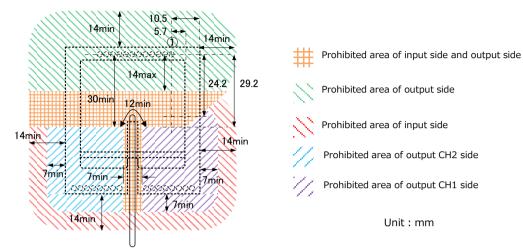

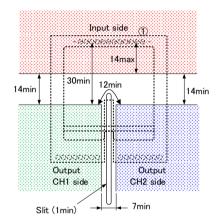

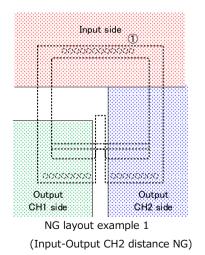

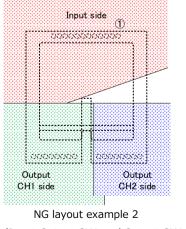

(3) Areas where components and wiring patterns may be placed

The peripheral areas of the module where components nor patterns may be placed are shown in the figure below. Ensure clearance and creepage with each section according to applicable safety standards.

Prohibited Area of the Application PCB

Recommended layout example 1

Recommended layout example 2

(Input-Output CH1 and Output CH1-CH2 distance NG)

\*Recommended value of Slit width · · · Pollution degree1 : 0.5mm or more / Pollution degree2 : 1.0mm or more

# 3.11 Handling

When handling, do not apply excessive stress to this product.

Do not handle or touch the product in an environment without ESD protection, as it may cause product failure and affect reliability.

## 3.12 Device short circuit

This product has DESAT protection for arm short circuit and load short circuit protection.

However, even if this protection works, the deivce may be damaged if abnormally high current occurs due to the deivce

characteristics variations or the load short-circuit mode during parallel operation.

To ensure safety, be sure to check the short-circuit current at the unit in which this product is integrated,

and evaluate whether it can protect under the condition that there is no damage to the device.

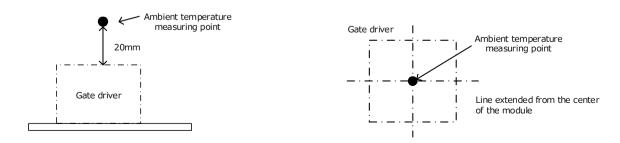

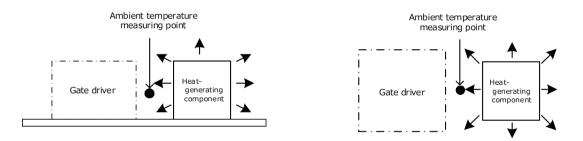

# 3.13 Ambient temperature instructions

The operating ambient temperature of the gate driver should be the temperature inside the set, and measure it as follows. If heat is generated from a peripheral component, the temperature of the heat should be regarded as the ambient temperature. If there is no heat-generating component around the gate driver, the temperature at a point that is 20 mm above the center of the gate driver case should be regarded as the ambient temperature.

Use according to the permissible frequency curve described in the data sheet for each product.

Use the gate driver board with a maximum surface temperature of 120 ° C or less.

<Point where the ambient temperature is measured if there is a heat-generating component near the module>

<Point where the ambient temperature is measured if there are no effects of heat-generating components>