# Gate Driver Unit 2DU180206MR02

#### **■**Overview

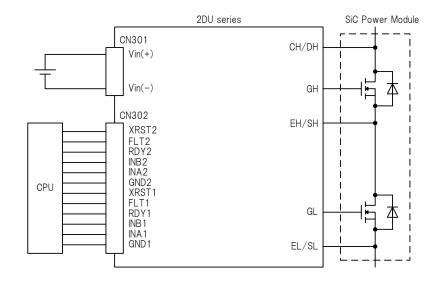

2DU180206MR02 is a dual channel gate driver designed for Rohm's SiC power module BSM300D12P3E005 / BSM400D12P3G002.

Built-in isolated DC / DC converter and gate drive circuit, in addition, gate resistor and short circuit detection voltage have already been set.

## **■**Features

- ·Ideal for drive of SiC Power module BSM300D12P3E005 / BSM400D12P3G002(ROH...,

- Gate resistor :  $2.2 \Omega$  (TYP)

- ·Short circuit detection voltage: 4.3V(TYP)

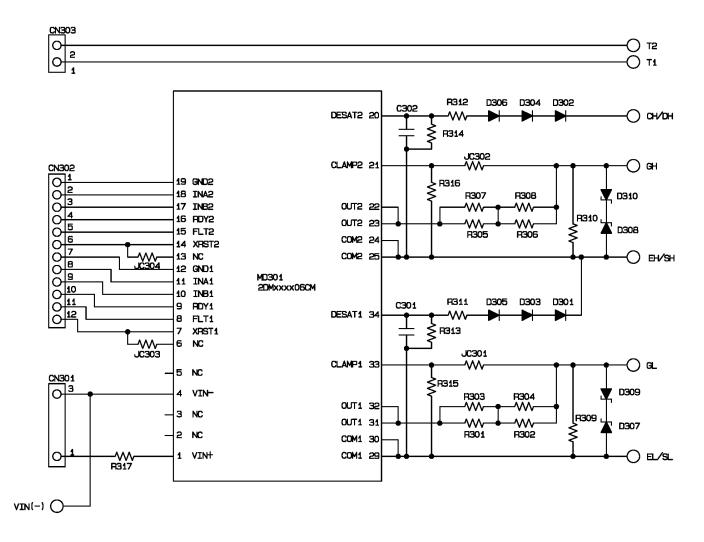

- ·Constitution: Gate driver module (2DM180206CM) + PCB for power module connection

- · ALL-IN-ONE (Built-in isolated DC / DC converter and gate drive circuit)

- ·Ideal for half bridge operation with dual output

- ·Optimum gate voltage for driving SiC-MOSFET(+18V/-2V) / BSM300D12P3E005 / BSM400D12P3G002(ROHM)

- ·Low parasitic capacitance (about 15pF); highly resistant to common-mode noise.

- ·Fast response : 100nsec(typ)

- •The gate drive circuit used a magnetic isolator.

- ·Dielectric withstand voltage: AC2500V (1 second guarantee)

- ·Insulation distance (clearance / creepage): 6mm/6mm

- ·DC/DC converter input voltage: 15~24V

- ·Signal input voltage: 5V

- ·Overload protection (DC/DC converter)

- Overheat protection (DC/DC converter)

- ·Desaturation protection (Gate drive circuit)

- ·Fault signal output function (Gate drive circuit)

- ·Miller clamp function (Gate drive circuit)

- ·Under-voltage lockout(UVLO) (Gate drive circuit)

- ·Filling structure

#### ■ Application

Industrial inverter, PV inverter, etc...

## **■**Ciruit Image

#### **■**Circuit Diagram

#### **■**Pin Connection

CN301: B2(3)B-EH(JST) For power supply

| Pin No. | Name   | Function                            |  |  |  |  |  |  |  |

|---------|--------|-------------------------------------|--|--|--|--|--|--|--|

| 1       | Vin(+) | Power supply for DC/DC converter(+) |  |  |  |  |  |  |  |

| 2       | N.C.   | Unused                              |  |  |  |  |  |  |  |

| 3       | Vin(-) | Power supply for DC/DC converter(-) |  |  |  |  |  |  |  |

CN302 : B12B-ZR-SM4-TF(JST) For signal

| Pin No. | Name  | CH   | Function                   |  |  |  |

|---------|-------|------|----------------------------|--|--|--|

| 1       | GND2  | 2(H) | Ground for control circuit |  |  |  |

| 2       | INA2  | 2(H) | Control input A            |  |  |  |

| 3       | INB2  | 2(H) | Control input B            |  |  |  |

| 4       | RDY2  | 2(H) | Ready output               |  |  |  |

| 5       | FLT2  | 2(H) | Fault output               |  |  |  |

| 6       | XRST2 | 2(H) | Reset input                |  |  |  |

| 7       | GND1  | 1(L) | Ground for control circuit |  |  |  |

| 8       | INA1  | 1(L) | Control input A            |  |  |  |

| 9       | INB1  | 1(L) | Control input B            |  |  |  |

| 10      | RDY1  | 1(L) | Ready output               |  |  |  |

| 11      | FLT1  | 1(L) | Fault output               |  |  |  |

| 12      | XRST1 | 1(L) | Reset input                |  |  |  |

Connection on the power module

| Name  | CH   | Explanation of pins          |  |  |  |  |  |  |

|-------|------|------------------------------|--|--|--|--|--|--|

| GL    | 1(L) | Gate connection, Low side    |  |  |  |  |  |  |

| EL/SL | 1(L) | Source connection, Low side  |  |  |  |  |  |  |

| CH/DH | 2(H) | Drain connection, High side  |  |  |  |  |  |  |

| GH    | 2(H) | Gate connection, High side   |  |  |  |  |  |  |

| EH/SH | 2(H) | Source connection, High side |  |  |  |  |  |  |

CN303: OPEN(B2B-ZR-SM4-TF(JST)) For thermistor

| 01100   | 0 . OI LIV | DZD ZIV OWI+ II (OOI)) I OI LIICIIIIISLOI |

|---------|------------|-------------------------------------------|

| Pin No. | Name       | Function                                  |

| 1       | TH         | For thermistor                            |

| 2       | TH         | For thermistor                            |

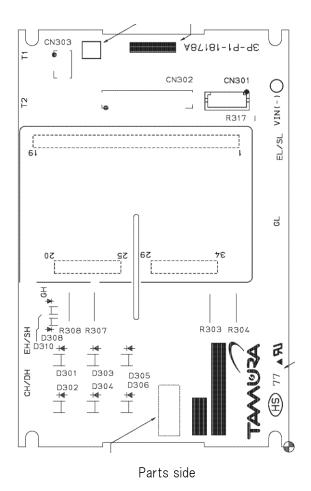

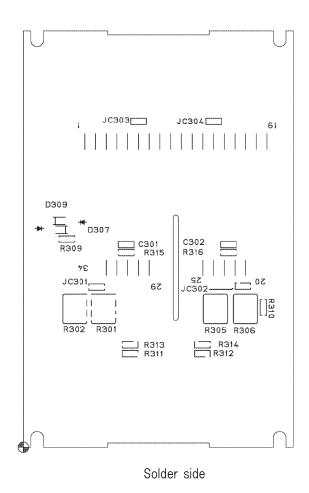

## ■Parts list

| Symbol    | Description        | Part No.       | Manufacturer | Remark               |

|-----------|--------------------|----------------|--------------|----------------------|

| D301-306  | Diode              | CMF05          | TOSHIBA      | Or equivalent        |

| D307-310  | Diode              | OPEN           |              | SOD-323              |

|           |                    |                |              |                      |

| C301,302  | Capacitor          | OPEN           |              | SMD1608              |

| D001 000  | D                  |                |              | 01400004             |

| R301-308  | Resistor           | 2.2 Ω J        |              | SMD3264              |

| R309,310  | Resistor           | 47kΩJ          |              | SMD1608              |

| R311,312  | Resistor           | 6.2k Ω J       |              | SMD1608              |

| R313-316  | Resistor           | OPEN           |              | SMD1608              |

| R317      | Resistor           | 0 Ω            |              | SMD2125              |

| JC301,302 | Jumper             | 0Ω             |              | SMD1608              |

| JC303,304 | Jumper             | OPEN           |              | SMD1608              |

| CN301     | Connector          | B2(3)B-EH      | JST          |                      |

| CN302     | Connector          | B12B-ZR-SM4-TF | JST          |                      |

| CN303     | Connector          | OPEN           |              | (B2B-ZR-SM4-TF(JST)) |

| MD301     | Gate Driver Module | 2DM180206CM    | TAMURA       |                      |

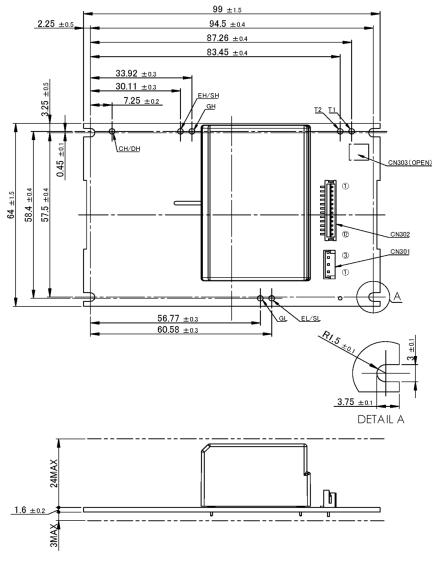

## ■Mouting Drawing

## ■I/O Condition Table

| No.  | Status                 |                   | Input             |       |      |     |     |       |     |       | put |      |

|------|------------------------|-------------------|-------------------|-------|------|-----|-----|-------|-----|-------|-----|------|

| INO. | Status                 | $V_{\text{5VDC}}$ | $V_{\text{OUTH}}$ | DESAT | XRST | INB | INA | CLAMP | OUT | CLAMP | FLT | RDY  |

| 1    |                        | 0                 | UVLO              | L     | Χ    | Χ   | Χ   | Н     | L   | Hi-Z  | Н   | L    |

| 2    | V <sub>outh</sub> UVLO | 0                 | UVLO              | L     | Χ    | Χ   | Χ   | L     | L   | L     | Η   | L    |

| 3    | VOUTH OVEO             | 0                 | UVLO              | Н     | Χ    | Χ   | Χ   | Н     | L   | Hi-Z  | L   | L    |

| 4    |                        | 0                 | UVLO              | Η     | Χ    | Χ   | Χ   | L     | L   | L     | L   | L    |

| 5    | DESAT                  | 0                 | 0                 | Н     | Χ    | Χ   | Χ   | Н     | L   | Hi-Z  | L   | H(*) |

| 6    | DESAT                  | 0                 | 0                 | Η     | Χ    | Χ   | Χ   | L     | L   | L     | L   | H(*) |

| 7    | XRST                   | 0                 | 0                 | L     | L    | Χ   | Χ   | Н     | L   | Hi-Z  | Η   | H(*) |

| 8    | XI\O I                 | 0                 | 0                 | L     | L    | Χ   | Χ   | L     | L   | L     | Н   | H(*) |

| 9    |                        | 0                 | 0                 | L     | Н    | Н   | Χ   | Н     | L   | Hi-Z  | Η   | H(*) |

| 10   | N. I                   | 0                 | 0                 | L     | Н    | Η   | Χ   | L     | L   | L     | Н   | H(*) |

| 11   | Normal operation       | 0                 | 0                 | L     | Н    | Г   | Ĺ   | Н     | Ĺ   | Hi-Z  | Н   | H(*) |

| 12   |                        | 0                 | 0                 | L     | Н    | L   | L   | L     | L   | L     | Н   | H(*) |

| 13   |                        | 0                 | 0                 | L     | Н    | L   | Н   | Χ     | Н   | Hi-Z  | Н   | H(*) |

O:5VDC or OUT(H) UVLO > UVLO, X:Don't care

## ■ Absolute Maximum Ratings

| Ito                               | em            | Symbol             | Min  | Max  | Unit | Conditions · Note        |

|-----------------------------------|---------------|--------------------|------|------|------|--------------------------|

| Input voltage for DC/DC converter |               | V <sub>IN</sub>    | -0.3 | 28   | Vdc  | Between Vin(+) to Vin(-) |

| Input-side signal volt            | age           | $V_{SG}$           | -0.3 | 5.2  | V    | INA, INB, XRST, RDY, FLT |

| Maximum gate charg                | 0             | $Q_{G}$            | 1    | 760  | nC   | BSM300D12P3E005 assumed  |

| INIAXIIIIUIII gate charg          | ᡛ             | $Q_{G}$            | _    | 1100 | nC   | BSM400D12P3G002 assumed  |

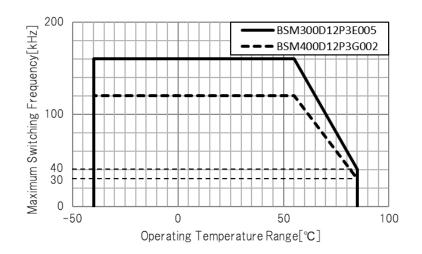

|                                   | Ta=55°C       | F <sub>SW</sub>    | -    | 160  | kHz  | Test load : 2.8 Ω / 39nF |

| Switching frequency               | Ta=85°C       | F <sub>SW</sub>    | _    | 40   | kHz  | BSM300D12P3E005 assumed  |

| Switching frequency               | Ta=55°C       | F <sub>SW</sub>    | -    | 120  | kHz  | Test load : 2.4Ω/55nF    |

|                                   | Ta=85°C       | F <sub>SW</sub>    | -    | 30   | kHz  | BSM400D12P3G002 assumed  |

| Short circuit detection           | n pin voltage | V <sub>SD</sub>    | 0    | 1000 | V    |                          |

| Maximum gate currer               | nt            | I <sub>GPEAK</sub> | -4.5 | 4.5  | Α    | Guaranteed by design     |

| Input-side signal max             | imum current  | I <sub>SG</sub>    | _    | 5    | mA   | RDY, FLT                 |

| Operating temperature range       |               | T <sub>OP</sub>    | -40  | 85   | °C   | See the derating curve   |

| Operating humidity                |               | RH <sub>OP</sub>   | 20   | 95   | %RH  | No condensation          |

| Storage temperature range         |               | $T_{STG}$          | -40  | 100  | °C   |                          |

| Storage humidity                  |               | RH <sub>STG</sub>  | 5    | 95   | %RH  | No condensation          |

## $\blacksquare$ Recommended Operating Conditons

| Item                                    | Symbol             | Min  | Max  | Unit | Conditions · Note                   |

|-----------------------------------------|--------------------|------|------|------|-------------------------------------|

| Input voltage range for DC/DC converter | V <sub>IN</sub>    | 13.5 | 26.4 | Vdc  |                                     |

| Driver circuit number                   | N                  | _    | 2    | -    |                                     |

| Logic high level input voltage          | $V_{SGH}$          | 2    | 5    | V    | INA, INB ,XRST                      |

| Logic low level input voltage           | $V_{SGL}$          | 0    | 0.8  | V    | INA, INB ,XRST                      |

| Source current of control signal        | I <sub>SG</sub>    | 20   | -    | mA   | INA, INB, XRST, V <sub>SG</sub> =5V |

| Minimum input pulse width               | t <sub>INMSK</sub> | _    | 60   | ns   |                                     |

<sup>(\*)</sup> If the internal logic of high voltage side doesn't become the expected value, the RDY pin will become "L". And this stage is cleared automatically if the internal logic of high voltage side becomes the expected value.

#### ■ Ambient Temperature Derating Curve

Reduce the switching frequency according to the following temperature derating table.

## ■Electrical Specification (Vin=24V, Ta=25°C, Unless otherwise specified)

#### DC/DC converter block

| ltem                                 | Symbol                            | Min  | Тур  | Max  | Unit | Conditions · Note                                                |

|--------------------------------------|-----------------------------------|------|------|------|------|------------------------------------------------------------------|

| Start-up voltage                     | $V_{START}$                       | -    | 11.5 | 12.5 | V    |                                                                  |

| Efficiency                           | Effi                              | 69   | 74   | _    | %    | I <sub>OUTAVE</sub> (CH1,2):100mA                                |

| Standby power                        | P <sub>STBY</sub>                 | -    | 0.7  | 1    | W    | No load                                                          |

| Output voltage(Hgih)                 | V <sub>1+</sub> ,V <sub>2+</sub>  | 17.5 | 18.5 | 19.5 | V    | $I_{OUTAVE}(CH1) = I_{OUTAVE}(CH2) = 10-150mA$                   |

| Output Voltage(Figili)               | v <sub>1+</sub> , v <sub>2+</sub> | 17.5 | 18.5 | 20.5 | V    | $I_{OUTAVE}(CH1) = I_{OUTAVE}(CH2) = 0-10mA$                     |

| Output voltage(Low)                  | V <sub>1-</sub> ,V <sub>2-</sub>  | -3   | -2   | -1   | V    | $I_{OUTAVE}(CH1) = I_{OUTAVE}(CH2) = 0-150mA$                    |

| Output Voltage(High)(Load imbalance) | V <sub>1+</sub> ,V <sub>2+</sub>  | -    | -    | 25   | V    | I <sub>OUTAVE</sub> (CH1):100mA,I <sub>OUTAVE</sub> (CH2):0mA    |

| Output Voltage(Low)(Load imbalance)  | V <sub>1-</sub> ,V <sub>2-</sub>  | -5   | -    | -    | V    | or I <sub>OUTAVE</sub> (CH1):0mA,I <sub>OUTAVE</sub> (CH2):100mA |

#### Gate drive block

|                         | ltem             | Symbol               | Min                    | Тур                      | Max                    | Unit | Conditions · Note        |

|-------------------------|------------------|----------------------|------------------------|--------------------------|------------------------|------|--------------------------|

| Logic                   |                  |                      |                        |                          |                        |      |                          |

| Logic high leve         | el input voltage | $V_{SGH}$            | 2                      | -                        | 5.2                    | V    | INA, INB ,XRST           |

| Logic low leve          | l input voltage  | $V_{SGL}$            | 0                      | _                        | 0.8                    | V    | INA, INB ,XRST           |

| Logic pull-dow          | n resistance     | $R_{SGD}$            | _                      | 270                      | -                      | Ω    | INA, INB ,XRST           |

| Logic pull-up r         | esistance        | R <sub>sgu</sub>     | ı                      | 5100                     | ı                      | Ω    | RDY, FLT                 |

| Logic input ma          | sk time          | t <sub>INMSK</sub>   | _                      | -                        | 60                     | ns   | INA, INB                 |

| Minimum XRST            | pulse width      | t <sub>XRSTMIN</sub> | 800                    | _                        | _                      | ns   |                          |

| Output                  |                  |                      |                        |                          |                        |      |                          |

| Output pin volt         | age(Hgih)        | V <sub>OUTH</sub>    | 1                      | V <sub>DCDCOH</sub> -0.5 | 1                      | V    | No load                  |

| Output pin volt         | age(Low)         | V <sub>OUTL</sub>    | 1                      | V <sub>DCDCOL</sub> +0.1 | 1                      | V    | No load                  |

| Gate resistor           |                  | Rg                   | ı                      | 2.2                      | 1                      | Ω    |                          |

| CLAMP ON res            | sistance         | R <sub>ONPRO</sub>   | 0.2                    | 0.5                      | 0.9                    | Ω    | I <sub>CLAMP</sub> =40mA |

| Low level CLAMP current |                  | I <sub>CLAMPL</sub>  | 3                      | 4.5                      | _                      | А    | Guaranteed by design     |

| CLAMP ON thr            | eshold voltage   | $V_{CLPON}$          | V <sub>OUTL</sub> +1.8 | V <sub>OUTL</sub> +2     | V <sub>OUTL</sub> +2.2 | V    | Guaranteed by design     |

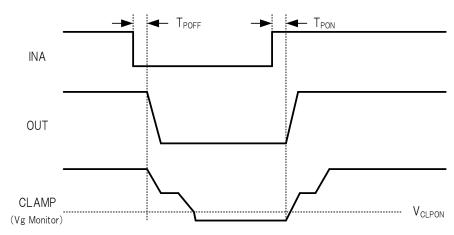

| Delay time              | Turn ON time     | t <sub>PON</sub>     | 50                     | 90                       | 130                    | ns   |                          |

| Delay tillle            | Turn OFF time    | t <sub>POFF</sub>    | 50                     | 90                       | 130                    | ns   |                          |

#### **■**Protection

## DC/DC converter block

| ltem                | Symbol | Min | Тур | Max | Unit | Conditions · Note    |

|---------------------|--------|-----|-----|-----|------|----------------------|

| Overload protection | _      | 6   | _   | _   | W    | Auto recovery        |

| Overheat protection | -      | 120 | -   | 150 | °C   | Internal temperature |

## Gate drive block

| ltem                            | Symbol                | Min  | Тур  | Max  | Unit | Conditions · Note       |

|---------------------------------|-----------------------|------|------|------|------|-------------------------|

| OUT(H) UVLO OFF voltage         | $V_{\text{UVLOOHH}}$  | 11.3 | 12.3 | 13.3 | V    | Guaranteed by design    |

| OUT(H) UVLO ON voltage          | $V_{\rm UVLOOHL}$     | 10.3 | 11.3 | 12.3 | V    | Guaranteed by design    |

| Short circuit detection voltage | $V_{SD}$              | _    | 4.3  | _    | V    | Guaranteed by design    |

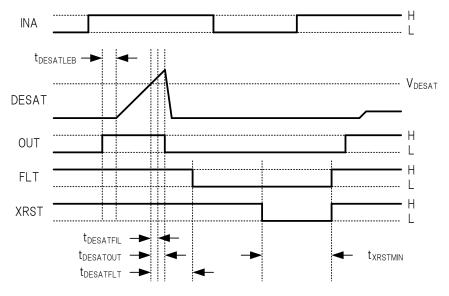

| DESAT filter time               | t <sub>DESATFIL</sub> | 0.16 | 0.25 | 0.34 | us   | Guaranteed by design    |

| DESAT delay time(OUT)           | t <sub>DESATOUT</sub> | 0.31 | 0.38 | 0.45 | us   | Guaranteed by design    |

| DESAT delay time(FLT)           | $t_{\text{DESATFLT}}$ | 0.34 | 0.42 | 0.5  | us   | Guaranteed by design    |

| DESAT low voltage               | $V_{DESATL}$          | -    | 0.1  | 0.22 | V    | I <sub>DESAT</sub> =1mA |

| DESAT leading edge blanking     | t <sub>DESTLEB</sub>  | 0.28 | 0.4  | 0.52 | us   | Guaranteed by design    |

| RDY output low voltage          | $V_{RDYL}$            | _    | 0.08 | 0.15 | V    | I <sub>RDY</sub> =5mA   |

| FLT output low voltage          | $V_{FLTL}$            | -    | 0.08 | 0.15 | V    | I <sub>FLT</sub> =5mA   |

## ■Insulation

| ltem                              | Specification | Conditions · Note |

|-----------------------------------|---------------|-------------------|

| Between Input-Output              | •             | <u> </u>          |

| Dielectric withstand voltage      | AC2500V       | 1min, Cutoff 2mA  |

| Test dielectric withstand voltage | AC2500V       | 1sec, Cutoff 2mA  |

| Insulation resistance             | 100MΩ or more | DC500V            |

| Minimum clearance distances       | 6mm MIN       |                   |

| Minimum creepage distances        | 6mm MIN       |                   |

| Between Ch1-Ch2                   | •             | •                 |

| Dielectric withstand voltage      | None          |                   |

| Test dielectric withstand voltage | None          |                   |

| Insulation resistance             | None          |                   |

| Minimum clearance distances       | 6mm MIN       |                   |

| Minimum creepage distances        | 6mm MIN       |                   |

#### ■Pin Function

- ·Vin(+), Vin(-) (Power supply pin for DC/DC converter)

- •GND(Ground pin for drive curcuit)

- ·INA, INB, XRST(Control input pin, XRST input pin)

The INA, INB and XRST pin is a pin used to determine output logic.

And, holding of the fault signal is canceled by rising of  $L \to H$  of the XRST pin input signal.

| XRST | INB | INA | OUT |

|------|-----|-----|-----|

| L    | Χ   | Χ   | L   |

| Н    | Н   | Χ   | L   |

| Н    | L   | L   | L   |

| Н    | L   | Н   | Н   |

#### •FLT(Fault output pin)

The FLT pin is an open drain pin used to output a fault signal when desaturation function is activated, and will be cleared at the rising edge of FLT.

| Status                                  |  |

|-----------------------------------------|--|

| While in normal operation               |  |

| When desaturation function is activated |  |

#### ·RDY(Ready output pin)

The RDY pin shows the status of three internal protection features which are 5VDC UVLO, OUT(H) UVLO, and output state feedback (OSFB). The term 'output state feedback' shows whether output internal logic is high or low corresponds to input logic or not.

| Status                                                     |  |

|------------------------------------------------------------|--|

| While in normal operation                                  |  |

| 5VDC UVLO or OUT(H) UVLO or Output internal logic feedback |  |

•GL(Low side MOSFET Gate connection pin)

GL is a land to be connected to the low side MOSFET gate of the power device.

·EL/SL(Low side MOSFET Source connection pin)

EL/SL is a land to be connected to the low side MOSFET source of the power device.

·CH/DH(High side MOSFET Drain connection pin)

CH/DH is a land to be connected to the high side MOSFET drain of the power device.

•GH(High side MOSFET Gate connection pin)

GH is a land to be connected to the high side MOSFET gate of the power device.

·EH/SH(Low side MOSFET Source connection pin)

EH/SH is a land to be connected to the high side MOSFET source of the power device.

#### **■**Description Of Protection

#### 1. Gate voltage rise prevention function

If OUT=L and the CLAMP pin voltage < VCLPON, the internal MOSFET of the CLAMP pin turns on.

| OUT | CLAMP                            | Internal MOSFET of the CLAMP pin |

|-----|----------------------------------|----------------------------------|

| L   | Less than $V_{\text{CLPON}}$     | ON                               |

| L   | Not less than V <sub>CLPON</sub> | OFF                              |

| Н   | Χ                                | OFF                              |

Timing chart of Miller clamp function

#### 2. Undervoltage Lockout (UVLO) function

The control circuit incorporates the undervoltage lockout (UVLO) function both on the OUT(H) sides. When the OUT(H) voltage drops to the UVLO ON voltage, the OUT pin and the RDY pin both will output the "L"signal. When the OUT(H) voltage rises to the UVLO OFF voltage, these pins will be reset. To prevent malfunctions due to noises, mask time  $t_{\text{UVLO1MSK}}$  and  $t_{\text{UVLO2MSK}}$  are set on both input and output sides.

## 3. Desaturation protection function(DESAT), Fault signal output function

When the DESAT pin voltage exceeds VDESAT, the DESAT function will be activated.

When the DESAT function is activated, the OUT pin voltage will be set to the "L" level, and then the FLT pin voltage to the "L" level. When the rising edge is put in the XRST pin, the DESAT function will be released.

**DESAT Operation Timing Chart**

#### ■Reliability

| ltem                                                               | Test condition and acceptance criterion                                                 |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| Exposure in high temperature                                       | 100°C, 240H, ※                                                                          |  |  |

| Exposure in low temperature                                        | -40°C, 240H, ※                                                                          |  |  |

| Exposure in high temperature and high humidity                     | 60°C, 90∼95%RH, 240H, ※                                                                 |  |  |

| Thermal shock                                                      | -40°C/30min to 100°C/30min, 500cycles, ※                                                |  |  |

| Low temperature operation                                          | Input voltage:DC24V, Output current:Rated Load                                          |  |  |

|                                                                    | -40°C, 240H, ※                                                                          |  |  |

| High temperature operation                                         | Input voltage:DC24V, Output current:Rated Load                                          |  |  |

|                                                                    | 85℃, 240H, ※                                                                            |  |  |

| high temperature                                                   | Input voltage:DC24V, Output current:Rated Load                                          |  |  |

| and high humidity operation                                        | 60°C, 90∼95%RH, 240H, ※                                                                 |  |  |

| Vibration                                                          | Vibration amplitude:1.5mm(peak to peak), Vibration Frequency:10 to 55Hz, Sweeping:1min. |  |  |

|                                                                    | In each X, Y and Z direction: once, 120min. ※                                           |  |  |

| Impact Acceleration:490m/s <sup>2</sup> (50G), Operating time:11ms |                                                                                         |  |  |

|                                                                    | In each $\pm X$ , Y and Z direction:3 times, $\divideontimes$                           |  |  |

| Drop test for packaged freights                                    | Dorp to concrete. Height: 40cm                                                          |  |  |

|                                                                    | Dorp surface: 1 corner, 3 spines, 6 surfaces, 1 time each.                              |  |  |

XAfter each test, exposure at room temperature and humidity condition for 24 hours.

There shall be no abnormality on the electrical specification and appearance.

#### **■**Outline Dimensional Drawing

Unit:mm

Note :1.The dimensional tolerance without directions is  $\pm$  0.5mm.

# ■Product Weight

96g(TYP)

#### ■Recommended Soldering Condition

·Soldering condition of hand work : 350°C(MAX) Less than 4sec

#### **■**Storage Conditions

| Item                | Min | Max | Unit | Conditions · Note |

|---------------------|-----|-----|------|-------------------|

| Storage temperature | -25 | 60  | °C   | A packing state   |

If you want to use past the long period there is a concern that the solder non-wetting by terminal oxidation to occur. Therefore, please use from taking enough tests.

#### **■**Usage Cautions

- Always mount fuse on the plus side of input for ensuring safety because the fuse is not built-in the product. Please select the fuse considering conditions such as steady current, inrush current, and ambient temperature. When using a fuse having large rated current or high capacity input electrolytic condenser, by combining another converter and input line and input electrolytic condenser, fuse may not blow off in the case of abnormality. Do not combine high voltage line and fuse.

- This product is designed to be best when it drives two devices to have the same gate capacitance simultaneously.

Because it leads to the "output unstable" and "output accuracy deterioration".

If you want to use to drive only one of the devices, because of the output voltage accuracy deterioration prevention,

please configure the dummy gate circuit (resistor and capacitor) to consume the equivalent of the power and the drive side.

- This product is to transmit the signal of the insulating part by the magnetic coupling.

Therefore, if you use this product in a strong magnetic field in, there is a possibility of malfunction.

In that case, connect the capacitor between the GND terminal of this product and a metal enclosure.

- Make sure the rise/fall time of the input signal is 500ns or less.

- Please confirm with the device supplier for the detail such as the screw type, material, torque force that tighten to device.

## **■**Important Notice

- The content of this information is subject to change without prior notice for the purpose of improvements, etc. Ensure that you are in possession of the most up-to-date information when using this product.

- The operation examples and circuit examples shown in this document are for reference purposes only, and TAMURA Corporation disclaims all responsibility for any violations of industrial property rights, intellectual property rights and any other rights owned by TAMURA Corporation or third parties that these may entail.

- The circuit examples and part constants listed in this document are provided as reference for the verification of characteristics. You are to perform design, verification, and judgment at your own responsibility, taking into account the various conditions.

- TAMURA has evaluated the efficiency and performance of this product in a usage environment determined by us.

Depending on your usage environment or usage method, there is the possibility that this product will not perform sufficiently as shown in the specifications, or may malfunction.

When applying this product to your devices or systems, please ensure that you conduct evaluations of their state when integrated with this product. You are responsible for judging its applicability.

- TAMURA bears no responsibility whatsoever for any problems with your devices, systems or this product which are caused by your usage environment or usage method.

- TAMURA Corporation constantly strives to improve quality and reliability, but malfunction or failures are bound to occur with some probability in power products. To ensure that failures do not cause accidents resulting in injury or death, fire accidents, social damage, and so on, you are to thoroughly verify the safety of their designs in devices and/or systems, at your own responsibility.

- This product is intended for use in consumer electronics (electric home appliances, business equipment, Information equipment, communication terminal equipment, measuring devices, and so on.) If considering use of this product in equipment or devices that require high reliability (medical devices, transportation equipment, traffic signal control equipment, fire and crime prevention equipment, aeronautics and space devices, nuclear power control, fuel control, in-vehicle equipment, safety devices, and so on), please consult a TAMURA sales representative in advance. Do not use this product for such applications without written permission from TAMURA Corporation.

- This product is intended for use in environments where consumer electronics are commonly used. It is not designed for use in special environments such as listed below, and if such use is considered, you are to perform thorough safety and reliability checks at your own responsibility.

- Use in liquids such as water, oil, chemical solutions, or organic solvents, and use in locations where the product will be exposed to such liquids.

- · Use that involves exposure to direct sunlight, outdoor exposure, or dusty conditions.

- · Use in locations where corrosive gases such as salt air, C12, H2S, NH3, S02, or NO2, are present.

- · Use in environments with strong static electricity or electromagnetic radiation.

- · Use that involves placing inflammable material next to the product.

- · Use of this product either sealed with a resin filling or coated with resin.

- · Use of water or a water soluble detergent for flux cleaning.

- · Use in locations where condensation is liable to occur.

- This product is not designed to resist radiation.

- This product is not designed to be connected in series or parallel.

Do not operate this product in a series, parallel, or N+1 redundant configuration.

- Do not use or otherwise make available the TAMURA products or the technology described in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of mass destruction weapons (e.g. nuclear, chemical, or biological weapons or missile technology products).

When exporting and re-exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations including, without limitation, Japan -Foreign Exchange and Foreign Trade Control Law and U.S.- Export Administration Regulations.

- The TAMURA products and related technology should not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- Please contact your TAMURA sales office for details as to environmental matters such as the RoHS compatibility of product.

Please use TAMURA products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive.

TAMURA assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- TAMURA assumes no liability for damages or losses incurred by you or third parties as a result of unauthorized use of TAMURA products.

- This document and any information herein may not be reproduced in whole or in part without prior written permission from TAMURA.